在无线通信、雷达探测、物联网和工业自动化等领域,信号识别是一项至关重要的技术,其核心任务是从接收到的复杂信号中提取关键特征,并准确判断其类型、调制方式或来源,传统信号识别方法高度依赖于专家设计的特征提取算法,面对日益复杂的电磁环境和多样化的信号类型,这些方法在泛化能力和准确性上逐渐显露出瓶颈,深度学习的崛起为这一领域带来了革命性的突破,它通过构建深层神经网络,能够自动学习信号中最具区分度的特征,从而实现更高精度和更强鲁棒性的识别。

深度学习赋能信号识别

深度学习模型,尤其是卷积神经网络(CNN)和循环神经网络(RNN),在处理信号数据方面展现出巨大潜力,对于通信信号,通常可以将其转换为时频图(如频谱图、星座图)或直接处理其时域采样序列。

卷积神经网络(CNN) 特别适合处理像频谱图这样的二维数据,CNN的卷积层能够像人类视觉系统一样,有效捕捉图像中的局部空间特征,如频谱图的纹理、形状和边缘,这些特征往往对应着特定的调制模式,通过多层卷积和池化操作,CNN可以逐步抽象出从低级到高级的特征表示,最终实现高精度的分类。

循环神经网络(RNN) 及其变体(如LSTM、GRU)则专为处理序列数据而设计,它们能够捕捉信号在时间维度上的依赖关系和动态变化规律,这对于分析具有时序特性的信号(如雷达脉冲、语音信号)至关重要,通过记忆单元,RNN可以“历史信息,从而更好地理解当前信号状态的上下文。

相比传统方法,基于深度学习的信号识别系统无需繁琐的人工特征工程,能够端到端地完成从原始信号到分类结果的映射,不仅大幅提升了识别准确率,也增强了对噪声和信道失真的鲁棒性。

FPGA:实现高效边缘部署的理想平台

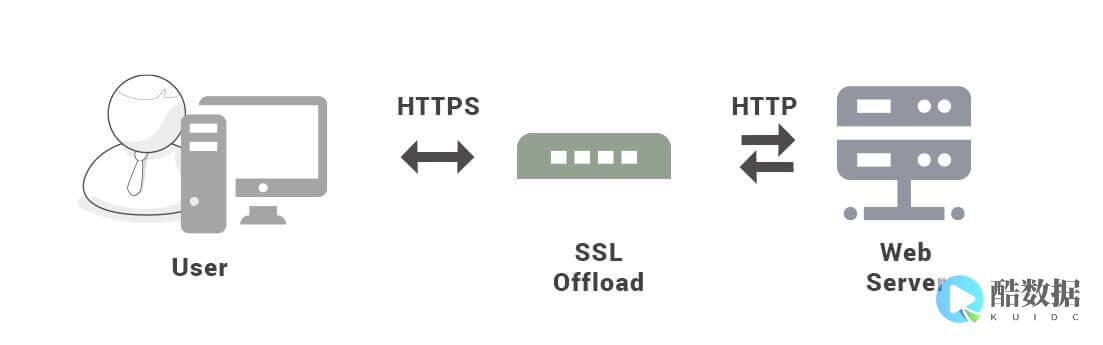

尽管深度学习模型功能强大,但其计算复杂度高、参数量巨大,对计算资源提出了严苛要求,在云端数据中心,可以利用高性能GPU集群进行模型训练和推理,在许多实际应用场景中,如无人机、车载系统、便携式设备等,对功耗、体积和实时性有着极为严格的限制,现场可编程门阵列(FPGA)便成为了理想的硬件加速平台。

FPGA是一种半定制电路,其内部包含可配置逻辑块、可编程连线和I/O单元,它允许开发者根据特定算法需求,自定义硬件电路结构,从而实现高度并行化的计算,这种特性使得FPGA在处理深度学习这类并行计算密集型任务时,具有天然的优势。

为了更直观地理解FPGA的定位,我们可以将其与其他主流硬件平台进行比较:

| 平台 | 灵活性 | 性能(并行计算) | 功耗 | 开发周期与成本 |

|---|---|---|---|---|

| 高 | 低 | 中 | 短,成本低 | |

| 中 | 高 | 高 | 中,成本中 | |

| 高 | 高 | 低 | 长,成本中 | |

| 极低 | 极高 | 极低 | 极长,成本极高 |

从上表可以看出,FPGA在性能、功耗和灵活性之间取得了绝佳的平衡,它不像GPU那样为通用图形计算设计而存在功耗冗余,也不像ASIC那样一旦流片便无法修改,FPGA的可重构性意味着它可以根据不同的深度学习模型或算法更新进行重新编程,适应快速变化的技术需求,同时其并行架构和低功耗特性使其成为边缘计算和嵌入式系统中部署深度学习模型的理想选择。

基于FPGA的深度学习信号识别实现流程

将一个深度学习信号识别模型成功部署到FPGA上,通常遵循一个系统化的流程:

应用场景与未来展望

基于FPGA的深度学习信号识别技术已在多个前沿领域展现出巨大的应用价值,在 认知无线电 中,它能实时监测频谱环境,智能识别空闲信道和干扰信号,实现动态频谱接入,在 电子战和雷达系统 中,它能快速识别敌方的雷达信号类型,为威胁评估和对抗策略提供决策支持,在 工业物联网 领域,它能通过分析电机振动、电流等传感器信号,实现设备故障的早期预测和诊断。

展望未来,随着AI专用硬件架构的不断演进和EDA工具链的日益成熟,基于FPGA的深度学习部署将变得更加高效和便捷,更轻量级的神经网络架构、更先进的量化算法以及支持在线学习的FPGA方案,将进一步拓展该技术在更多场景下的应用,推动智能信号处理向更边缘、更实时、更高效的方向发展。

相关问答 (FAQs)

Q1: 既然GPU在深度学习领域非常流行,为什么在信号识别等边缘应用中要选择FPGA而不是GPU?

GPU和FPGA各有优势,适用于不同场景,GPU拥有强大的并行计算能力和成熟的软件生态,非常适合大规模模型训练和云端推理,对于资源受限的边缘应用,FPGA的优势更为突出: 功耗更低 ,FPGA可以按需定制计算单元,避免了GPU的通用性带来的功耗浪费; 延迟更低且确定性 ,FPGA的硬件并行流水线结构能提供微秒级的稳定延迟,而GPU的操作系统和内存管理可能引入延迟抖动; 体积和成本优势 ,对于特定任务,FPGA可以设计得更紧凑,综合成本效益更高,在对功耗、实时性和体积有严格要求的嵌入式信号识别系统中,FPGA是更理想的选择。

Q2: 将深度学习模型部署到FPGA上,最大的技术挑战是什么?

最大的挑战在于如何 在保持模型精度的前提下,将其高效地映射到FPGA有限的硬件资源上 ,这个过程涉及多个层面:一是 模型优化 ,需要通过量化、剪枝等技术大幅压缩模型,但不当的压缩会导致精度显著下降,需要在模型大小和精度之间仔细权衡;二是 硬件实现 ,需要利用HLS等工具将算法逻辑转换为高效的硬件电路,这要求开发者对FPGA架构和并行计算有深入理解,以最大化资源利用率和吞吐率;三是 工具链的复杂性 ,虽然现代工具已大大简化了流程,但从模型转换到综合、实现、调试,整个流程仍然比纯软件开发复杂,需要软硬件协同设计的能力。

发表评论